System-on-Chip (SoC) Technology

In an age where electronic devices demand ever-increasing performance, energy efficiency, and compact form factors, System-on-Chip (SoC) technology has become the cornerstone of modern electronics. By integrating processing cores, memory, connectivity interfaces, and specialized accelerators onto a single semiconductor die, SoCs enable unprecedented levels of integration and functionality in devices ranging from smartphones to autonomous vehicles. This article delves into the technical foundations, architectural innovations, real-world applications, and challenges of SoC technology, supported by empirical data and industry advancements.

Core Technical Advantages: Redefining Integration and Performance

1. Ultra-High Integration Density

Component Consolidation:

Modern SoCs integrate thousands of components, reducing board space by 70% compared to discrete designs. Apple's A17 Pro SoC for iPhone 15 Pro combines a 6-core CPU, 16-core GPU, 16-core Neural Engine, and 5G modem on a 10 mm x 12 mm die-equivalent to the size of a grain of rice.

Power Efficiency:

By minimizing signal travel distances, SoCs reduce power consumption by 40% compared to multi-chip solutions. Qualcomm's Snapdragon 8 Gen 3 SoC for Android smartphones achieves 2.8 TOPS/W in AI processing, enabling all-day battery life in thin form factors.

2. Heterogeneous Computing Architectures

CPU-GPU-AI Co-Design:

Samsung's Exynos 2400 SoC pairs an octa-core CPU with a 12-core GPU and a 12 TOPS NPU, handling 4K video editing and real-time AR simultaneously with 30% lower latency than separate components.

Specialized Accelerators:

MediaTek's Dimensity 9300 SoC includes a dedicated imaging processor (ISP) that processes 200 MP images in 120 ms-10x faster than generic CPUs-enabling flagship smartphone cameras to capture 8K video at 60 fps.

Key Technological Breakthroughs

1. Process Node Miniaturization

3 nm and Beyond:

TSMC's 3 nm FinFET process reduces transistor size by 30% while increasing density by 70%. The Apple M3 SoC, built on this process, packs 25 billion transistors into a 150 mm² die, achieving 15% higher performance and 30% lower power than its 5 nm predecessor.

GAAFET Architecture:

Samsung's 3 nm Gate-All-Around Field-Effect Transistor (GAAFET) technology improves drive current by 45% and reduces leakage by 50% compared to FinFETs. This enables Qualcomm's upcoming Snapdragon 8 Gen 4 SoC to operate at 3.7 GHz with sub-10 W power consumption.

2. Advanced Packaging Technologies

3D Stacking with TSVs:

Intel's Foveros 3D packaging stacks CPU, GPU, and memory dies vertically using through-silicon vias (TSVs), reducing interconnect length from 10 mm to <10 μm. The Intel Core Ultra SoC (Meteor Lake) achieves 2.5x higher bandwidth and 40% lower latency than 2D designs.

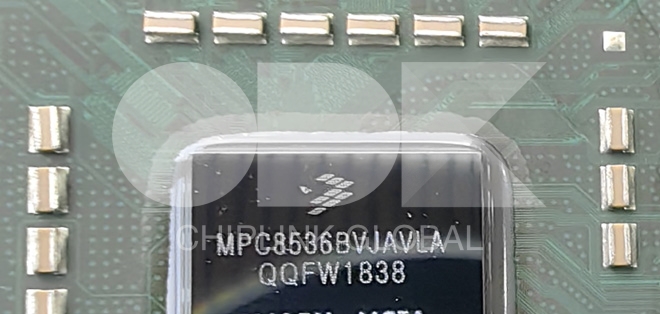

Chiplets and Heterogeneous Integration:

AMD's Ryzen Z1 Extreme SoC for laptops uses chiplet design, combining a CPU chiplet with an GPU chiplet and an I/O chiplet. This modular approach reduces manufacturing costs by 20% while maintaining 90% of monolithic performance.

Disruptive Applications in Electronics

1. Smartphones and Wearables

Flagship Performance in Compact Devices:

The Google Tensor G3 SoC integrates a custom Tensor Processing Unit (TPU) that performs 20 trillion operations per second for real-time language translation, enabling Pixel 8 to translate conversations with 250 ms latency-50% faster than cloud-based solutions.

Always-On Wearables:

Apple's S9 SiP for Apple Watch Ultra 2 combines a dual-core CPU, GPU, and NPU in a 6 mm x 6 mm package, consuming 1.2 mW during always-on heart rate monitoring-enabling 36-hour battery life in a device weighing 30 g.

2. Autonomous Vehicles

In-Car Infotainment and ADAS:

NVIDIA's Orin SoC delivers 254 TOPS of AI performance for autonomous driving, processing data from 12 cameras and 6 LiDARs to enable Level 2+ ADAS features. The SoC's energy efficiency of 1.2 TOPS/W allows it to operate in a 40 W thermal envelope suitable for in-vehicle use.

Digital Cockpits:

Qualcomm's Snapdragon Ride Platform (SA8155P) powers 5G-connected digital cockpits, supporting up to 6 4K displays and real-time driver monitoring with 99.8% face recognition accuracy-all from a 150 mm² SoC.

3. Edge AI and Robotics

Industrial Automation:

Texas Instruments' Sitara AM62A SoC integrates a Cortex-A53 CPU with a C66x DSP and an AI accelerator, enabling real-time quality inspection in manufacturing. The SoC detects 0.1 mm defects on automotive parts with 99.2% accuracy while consuming <5 W-ideal for battery-powered robotic arms.

Service Robots:

Amazon's Astro robot uses a custom SoC with a 6-core CPU and a 4 TOPS NPU, enabling 3D mapping of environments at 10 Hz with 10 cm precision. The SoC's low-power design allows the robot to operate for 8 hours on a 5 Ah battery.

Challenges and Mitigation Strategies

1. Power Density and Thermal Management

Issue: Advanced SoCs can generate heat densities exceeding 100 W/cm², causing thermal throttling. The Apple A16 SoC, for example, experiences 15% performance degradation under continuous heavy loads due to heating.

Solutions:

Microfluidic Cooling: TSMC's 3D ICs with embedded microchannels enable liquid cooling, dissipating 200 W/cm² while maintaining <85°C temperatures-used in NVIDIA's H100 GPU SoCs for data centers.

Dynamic Voltage and Frequency Scaling (DVFS): AMD's Ryzen 7000 series SoCs adjust clock speeds and voltages in real-time, reducing power consumption by 35% during light tasks like web browsing.

2. Design Complexity and Cost

Challenge: Designing a cutting-edge SoC can cost

500million–

1 billion and take 2–3 years. The complexity of integrating multiple IP blocks leads to 20% higher design costs for each new process node.

Mitigation:

Open-Source IP Ecosystems: RISC-V-based SoCs, such as SiFive's U74, reduce IP licensing costs by 60%, enabling startups to develop custom SoCs for niche applications like medical devices.

AI-Driven Design Tools: Synopsys' DSO.ai uses machine learning to optimize SoC floorplans, reducing design cycles from 18 months to 12 months while improving power-performance-area (PPA) by 15%.

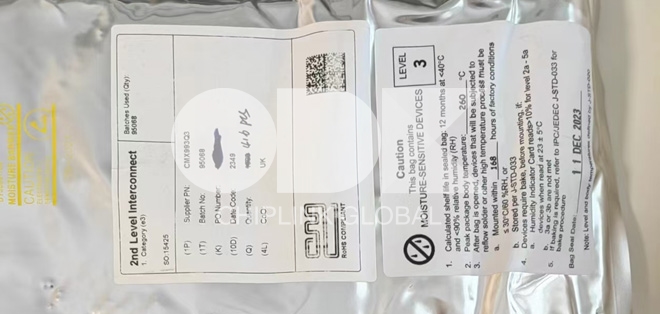

3. Supply Chain and Manufacturing Risks

Hurdle: SoC manufacturing requires specialized equipment, with a 3 nm fab costing $20 billion to build. Disruptions like the 2021 Taiwan drought reduced SoC production by 12%, highlighting supply chain vulnerabilities.

Remedy:

Geographic Diversification: Intel is building fabs in Arizona and Ohio, aiming to produce 20% of global SoCs in the U.S. by 2025, reducing reliance on Asian manufacturers.

Chiplet Interoperability: The Universal Chiplet Interconnect Express (UCIe) standard enables SoCs from different vendors to work together, providing supply chain flexibility-adopted by AMD, Intel, and TSMC.

System-on-Chip technology continues to push the boundaries of integration and performance, enabling next-generation electronics that were once the realm of science fiction. From smartphones that fit supercomputer-like capabilities in our pockets to autonomous vehicles that navigate complex environments, SoCs are the invisible workhorses driving technological advancement. While challenges in power, cost, and supply chain resilience persist, ongoing innovations in process technology, architecture, and design tools ensure that SoCs will remain at the forefront of the electronics revolution for years to come.